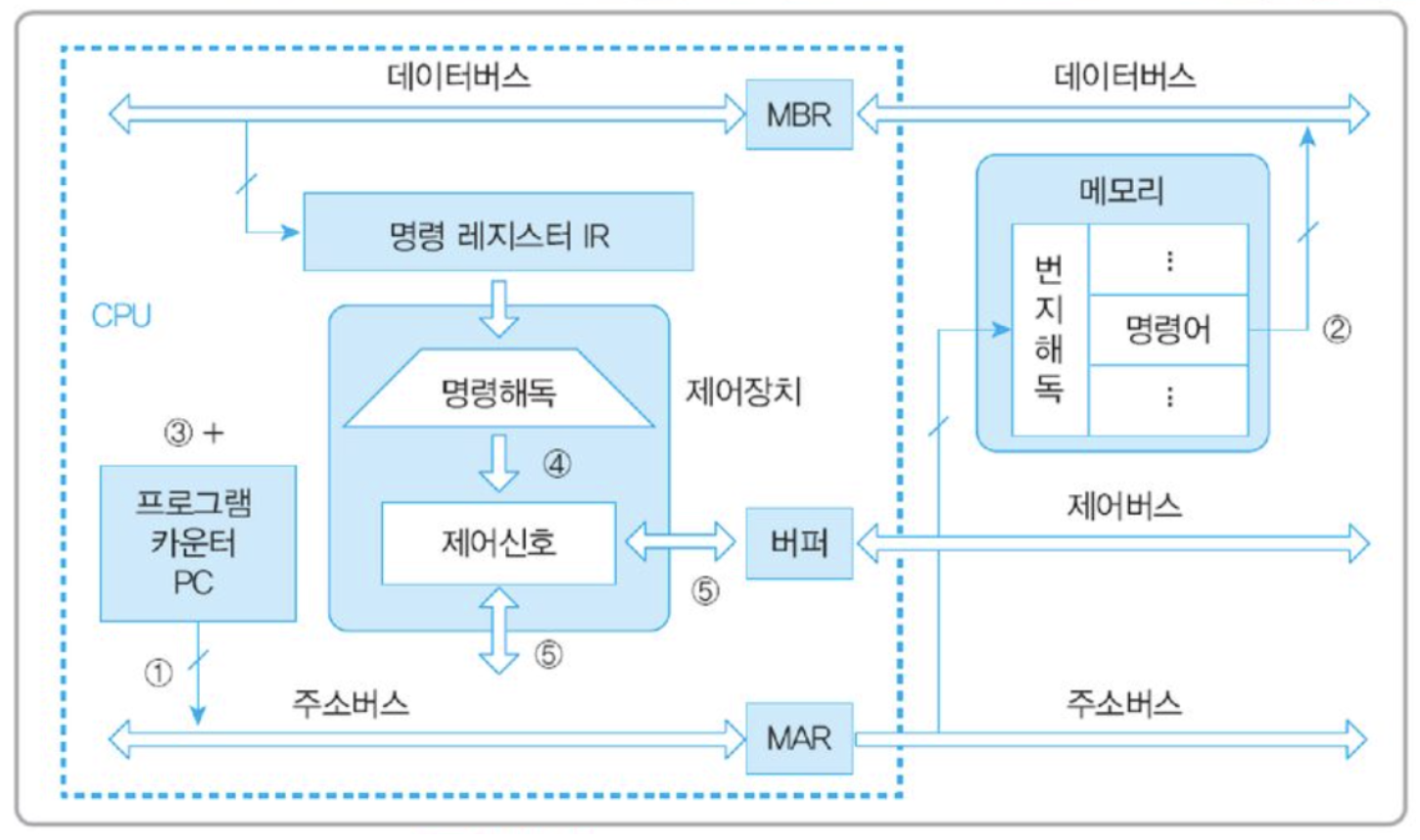

CPU는 크게

연산장치, 제어장치, 레지스터 로 구성됩니다.

- 연산장치

- 산술연산, 논리연산 등을 수행

- 제어장치

- 명령어를 순서대로 실행할 수 있게 제어

- 인출, 해독, 실행 단계로 나누어짐

- 레지스터

- 고속 기억장치

- 명령어 주소, 데이터, 연산결과 등을 저장

특수 목적 레지스터

- PC(프로그램 카운터) : 다음 실행할 명령어 주소 저장

- MAR(메모리 주소 레지스터) : 읽기와 쓰기 연산을 수행할 주기억장치 주소 저장

- MBR(메모리 버퍼 레지스터) : 주기억장치에서 읽어온, 저장할 데이터 저장

- IR(명령어 레지스터) : 현재 실행 중인 명령어 저장

- AC(누산기) : 연산 결과 저장

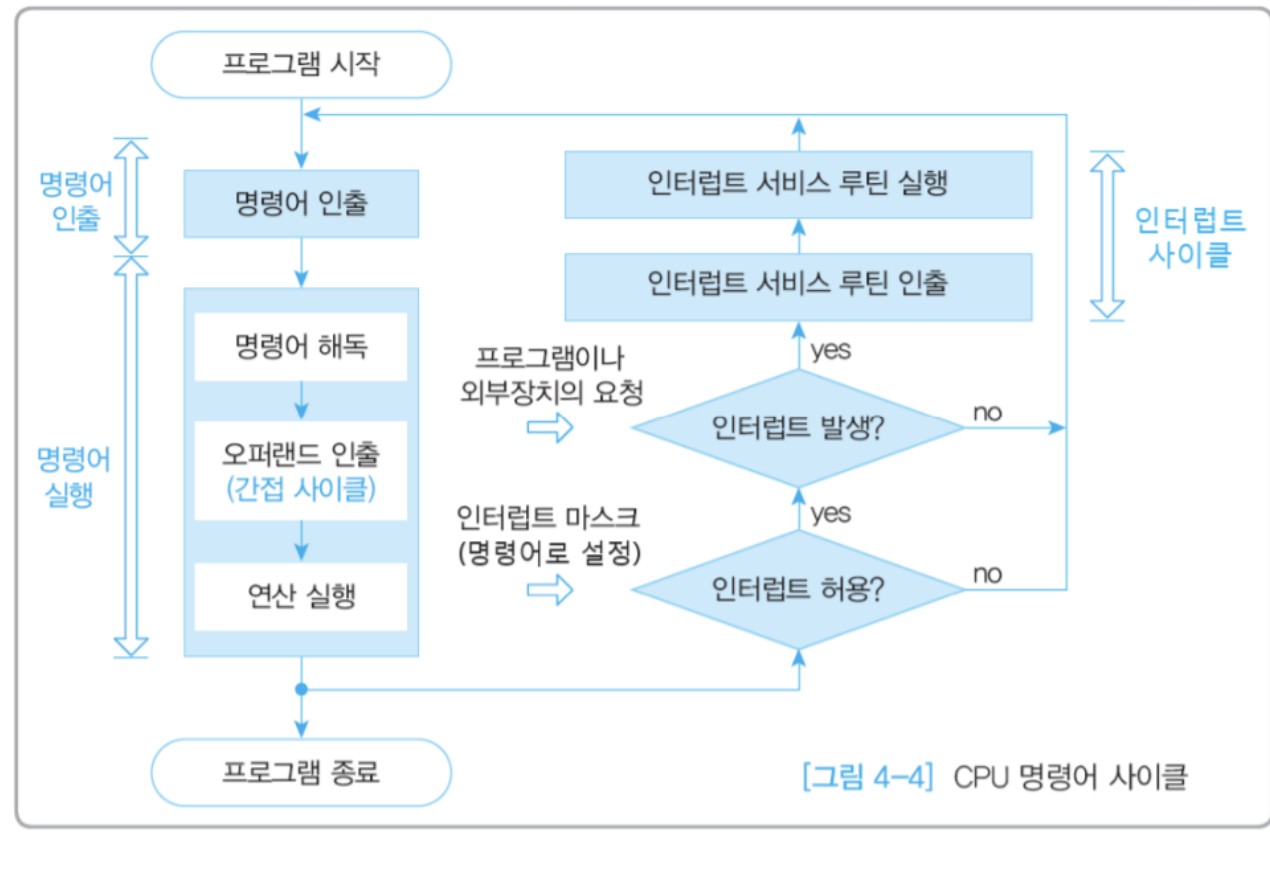

명령어 사이클

명령어 인출

t1 : MAR ← PC

t2 : MBR ← M[MAR] , PC ← PC + 1

t3 : IR ← MBR

명령어 해독

t1 : Decoder ← (IR : opcode)

t2 : 명령어 해독 , Instruction Decoding (제어신호 발생)

명령어 실행

t1 : MAR ← (IR : operand), MBR ← PC

t2 : MBR ← M[MAR]

t3 : R1(레지스터) ← MBR

인터럽트 사이클

인터럽트

t1 : MAR ←SP, MBR ← PC

t2 : M[MAR] ← MBR, SP ← SP-1

t3 : PC ← ISR

'Computer Science' 카테고리의 다른 글

| 인터럽트란? (Interrupt) (0) | 2022.06.29 |

|---|---|

| 프로세스와 스레드의 차이 (0) | 2022.06.14 |

| 파이프라인이란? (0) | 2022.06.09 |

| 메모리 구조 (Memory structure) - code, data, heap, stack (0) | 2022.06.02 |

| 캐시(cache) 란 무엇인가? (0) | 2022.05.31 |